The eviction of memory block from the cache is decided by the replacement policy.If the cache is completely occupied then a block is evicted and the memory block is placed in that cache line.

If the valid bit is 0, the new memory block can be placed in the cache line, else it has to be placed in another cache line with valid bit 0.

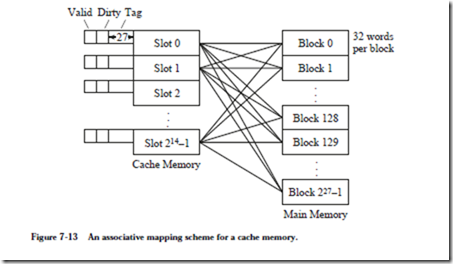

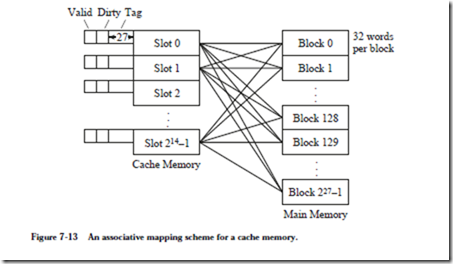

The cache line is selected based on the valid bit associated with it. The cache organization can be framed as (1*m) row matrix. A memory block can occupy any of the cache lines. In a Fully associative cache, the cache is organized into a single cache set with multiple cache lines. Similarly, address 0x00FF(tag – 00_0000, index – 11_1111, offset – 11) maps to block 63 of the memory and occupies the set 63 of the cache.Īddress 0x0100(tag – 00_0001, index – 00_0000, offset – 00) maps to block 64 of the memory and occupies the set 0 of the cache. In the example, the tag bits are 6 (14 – (6+2)), which are stored in tag field to match the address on cache request.Īddress 0x0000(tag - 00_0000, index – 00_0000, offset – 00) maps to block 0 of the memory and occupies the set 0 of the cache.Īddress 0x0004(tag - 00_0000, index – 00_0001, offset – 00) maps to block 1 of the memory and occupies the set 1 of the cache. In the example, the index bits are 6 which are used to address the 64 sets of the cache. Index corresponds to bits used to determine the set of the Cache. In the example, the offset bits are 2 which are used to address the 4 bytes of the cache line. Offset corresponds to the bits used to determine the byte to be accessed from the cache line. The incoming address to the cache is divided into bits for Offset, Index and Tag. Since each cache block is of size 4 bytes, the total number of sets in the cache is 256/4, which equals 64 sets. Ĭonsider Main memory of 16 Kilobytes, which is organized as 4-byte blocks and Cache of 256 bytes with block size of 4 bytes. Every time a new memory is referenced to the same set, the cache line is replaced, which causes conflict miss. It has lower cache hit rate, as there is only one cache line available in a set. It requires cheap hardware as only one tag needs to be checked at a time. The placement policy and the replacement policy is simple. This placement policy is power efficient as it avoids the search through all the cache lines. Else there is a cache miss and the memory block is fetched from the lower memory(main memory, disk). If the tag matches, then there is a cache hit and the cache block is returned to the processor. The tag bits derived from the memory block address are compared with the tag bits associated with the set. The set is identified by the index bits of the address. If the cache line is previously occupied, then the new data replaces the memory block in the cache. The memory block is placed in the set identified and the tag is stored in the tag field associated with the set. The set is determined by the index bits derived from the address of the memory block. The cache can be framed as a (n*1) column matrix. Based on the address of the memory block, it can only occupy a single cache line. By sending to four lines per set, the number of sets is decreased to 128 sets needing 7 bits to recognize the set and twenty bits for the tag.In a direct mapped cache structure, the cache is organized into multiple sets with a single cache line per set.

This can leave 30 – 8 – 3 = 19 bits for the tag. In the instance of the cache having 512 lines, we can achieve 256 sets of two lines each, which would require eight bits from the memory address to recognize the set. In a direct mapping scheme, this can leave 30 – 9 – 3 = 18 bits for the tag.īy sending from direct mapping to set associative with a set size of two lines per set, the various sets achieved equals half the number of lines.

Direct mapped vs set associative full#

Because the mapping approach uses the memory address only like direct mapping does, the number of lines included in a set should be similar to an integer power of two, for example, two, four, eight, sixteen, etc.Įxample − Consider a cache with 2 9 = 512 lines, a block of memory contains 2 3 = 8 words, and the full memory space includes 2 30 = 1G words. The diagram represents this arrangement using a sample cache that uses four lines to a set.Ī set-associative cache that includes k lines per set is known as a k way set-associative cache. However, the lines within each set are treated as a small fully associative cache where any block that can save in the set can be stored to any line inside the set.

The sets are persistent using a direct mapping scheme. Set associative mapping combines direct mapping with fully associative mapping by arrangement lines of a cache into sets.

0 kommentar(er)

0 kommentar(er)